# **Digital Controlled Variable Gain Amplifier**

50Ω 0.45 to 2.4 GHz 31.5 dB, 0.5 dB Step, 6 Bit Serial Control

# The Big Deal

- Integrated Amplifier and Digital Attenuator

- 30 dB Gain / 31.5 dB Gain Control

- High Output IP3, 34-37 dBm

CASE STYLE: DG1677

# **Product Overview**

The DVGA1-242+ is a  $50\Omega$  RF Digital Variable Gain Amplifier that offers an attenuation of 31.5 dB in 0.5 dB steps using a 6-bit serial interface attenuator and 30dB gain using a E-PHEMT amplifier. Step attenuator used in DVGA1-242+ is produced using a unique combination of CMOS process on silicon, offering the performance of GaAs, with the advantages of conventional CMOS devices.

# **Key Features**

| Feature                                                                        | Advantages                                                                                                                                                                                                     |

|--------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31.5 dB attenuation in 0.5 dB step size                                        | Combining high gain and a wide range of gain control makes the DVGA1-242+<br>an ideal building block for any RF chain where level setting control is required in a<br>small space.                             |

| High Gain, 30 dB                                                               | Incorporating multiple stages of amplification, the DVGA1-242+ provides high gain reducing cost and PCB board space                                                                                            |

| High IP3, +34 dBm at 1.0 GHz<br>Low Noise Figure, 2.5 dB at 1.0 GHz            | Combining Low Noise and High IP3 makes this MMIC amplifier ideal for Low Noise Receiver Front End (RFE) giving the user advantages at both ends of the dynamic range: sensitivity & two-tone IM dynamic range. |

| Output Power, +23 dBm at 2.4 GHz                                               | The DVGA1-242+ maintains consistent output power capability over the full operat-<br>ing temperature range making it ideal to be used in remote applications such as<br>LNB's as the L Band driver stage.      |

| MCLP Package                                                                   | Low Inductance, repeatable transitions, excellent thermal pad.                                                                                                                                                 |

| Max Input Power, +24 dBm                                                       | Ruggedized design operates up to input powers often seen at Receiver inputs.                                                                                                                                   |

| Attenuation Step size, 0.5 dB, accuracy 0.1 dB typ. Total attenuation, 31.5 dB | Enables precise control of gain in 0.5 dB steps up to 31.5 dB.                                                                                                                                                 |

| External Jumper                                                                | Customer access is provided between the digital attenuator and the RF amplifier to allow the user to integrate external circuit elements if desired.                                                           |

A Performance and quality attributes and conditions not expressly stated in this specification document are intended to be excluded and do not form a part of this specification document. B. Electrical specifications and performance data contained in this specification document are based on Min-Circuit's applicable established test performance criteria and measurement instructions. C. The parts covered by this specification document are subject to Min-Circuit's transformantly and terms and conditions (collectivity, "Standard Terms"); Purchasers of this part are entitled to the rights and benefits contained therein. For a full statement of the Standard Terms and the exclusive rights and remedies thereunder, please visit Mini-Circuits' website at www.minicircuits.com/MCLStore/terms.jsp

# Digital Controlled Variable Gain Amplifier

50Ω 450-2400 MHz

30 dB Gain, 0.5 dB Step, 31.5 dB Attenuation, 6 Bit Serial Control

## **Product Features**

- 31.5 dB Gain control 0.5dB step size

- Gain, 30 dB nominal at 0dB attenuation and 1 GHz

- Excellent accuracy, 0.1 dB typ

- Serial control interface

- Small size 5.0 x 5.0 mm

+RoHS Compliant The +Suffix identifies RoHS Compliance. See our web site for RoHS Compliance methodologies and qualifications

## **Typical Applications**

- Base Station Infrastructure

- GPS

- LTE

- WCDMA

### **General Description**

The DVGA1-242+ is a  $50\Omega$  RF Digital Variable Gain Amplifier that offers an attenuation of 31.5 dB in 0.5 dB steps using a 6-bit serial interface attenuator and 30dB gain using a E-PHEMT amplifier. Step attenuator used in DVGA1-242+ is produced using a unique combination of CMOS process on silicon, offering the performance of GaAs, with the advantages of conventional CMOS devices.

A Performance and quality attributes and conditions not expressly stated in this specification document are intended to be excluded and do not form a part of this specification document. B. Electrical specifications and performance data contained in this specification document are based on Nini-Circuit's applicable established test performance criteria and measurement instructions. C. The parts covered by this specification document are subject to Mini-Circuit standard limited warranty and terms and conditions (collectively, "Standard Terms"). Purchasers of this part are entitled to the rights and benefits contained therein. For a full statement of the Standard Terms and the exclusive rights and remedies thereunder, please visit Mini-Circuit's website at www.minicircuits.com/WCLStore/terms.jsp

REV. A M139026 DVGA1-242+ 130319 Page 2

# Mini-Circuits

# Digital Controlled Variable Gain Amplifier (DVGA)

| Parameter                             | Condition (GHz) | Min. | Тур.       | Max. | Units |  |

|---------------------------------------|-----------------|------|------------|------|-------|--|

| Frequency Range                       |                 | 0.45 |            | 2.4  | GHz   |  |

|                                       | .45             | —    | 29.0       | —    |       |  |

|                                       | 1.0             | -    | 30.3       | _    |       |  |

| Gain (at 0 dB attenuation)            | 1.4             | 26.5 | 29.5       | 32.4 | dB    |  |

|                                       | 2.0             | -    | 24.4       | _    |       |  |

|                                       | 2.4             |      | 21.0       | —    |       |  |

|                                       | .45             | _    | 15.4       | —    |       |  |

|                                       | 1.0             | -    | 15.1       | _    |       |  |

| Input Return Loss (all states)        | 1.4             | _    | 9.5        | —    | dB    |  |

|                                       | 2.0             | _    | 9.5        | —    |       |  |

|                                       | 2.4             |      | 14<br>19.5 |      |       |  |

|                                       | .45             | _    | 19.5       | _    |       |  |

| Output Return Loss (all states)       | 1.4             |      | 10.7       |      | dB    |  |

| Sulput Heldin Loss (all states)       | 2.0             |      | 9.5        |      | UD    |  |

|                                       | 2.0             |      | 9.0        |      |       |  |

|                                       | .45             | _    | 22.5       |      |       |  |

|                                       | 1.0             | _    | 22.8       | _    |       |  |

| Output Power @ 1 dB compression       | 1.4             | 20.0 | 23.2       | _    | dBm   |  |

| (at min and max attenuation)          | 2.0             | _    | 23.2       | _    |       |  |

|                                       | 2.4             | _    | 23.0       | _    |       |  |

|                                       | .45             | _    | 35.2       | _    | dBm   |  |

|                                       | 1.0             |      | 34.5       | _    |       |  |

| Output IP3 (all states)               | 1.4             | -    | 35.7       | _    |       |  |

|                                       | 2.0             | _    | 37.0       | _    |       |  |

|                                       | 2.4             |      | 37.0       |      |       |  |

|                                       | .45             | _    | 3.8        | —    |       |  |

|                                       | 1.0             |      | 2.5        |      |       |  |

| Noise Figure (at 0 dB attenuation)    | 1.4             | -    | 3.1        | 3.7  | dB    |  |

|                                       | 2.0             | _    | 3.4        | —    |       |  |

|                                       | 2.4             |      | 3.5        |      |       |  |

| Accuracy @ 0.5 dB Attenuation Setting | .45 - 1.0       |      | 0.05       | 0.12 | dB    |  |

|                                       | 1.0 - 2.4       |      | 0.08       | 0.18 |       |  |

| Accuracy @ 1 dB Attenuation Setting   | .45 - 1.0       |      | 0.04       | 0.13 | dB    |  |

|                                       | 1.0 - 2.4       |      | 0.11       | 0.2  |       |  |

| Accuracy @ 2 dP Attenuation Setting   | .45 - 1.0       | _    | 0.12       | 0.25 | dB    |  |

| Accuracy @ 2 dB Attenuation Setting   | 1.0 - 2.4       | _    | 0.24       | 0.37 | UD    |  |

|                                       | .45 - 1.0       | _    | 0.19       | 0.37 |       |  |

| Accuracy @ 4 dB Attenuation Setting   | 1.0 - 2.4       | _    | 0.27       | 0.45 | dB    |  |

|                                       | .45 - 1.0       | _    | 0.22       | 0.4  | dB    |  |

| Accuracy @ 8 dB Attenuation Setting   | 1.0 - 2.4       |      | 0.37       | 0.7  |       |  |

|                                       | .45 - 1.0       |      | 0.32       | 0.6  | dB    |  |

| Accuracy @ 16 dB Attenuation Setting  | 1.0 - 2.4       |      | 0.88       | 1.2  |       |  |

### RF Electrical Specifications<sup>(1)</sup> at 25°C, 50 $\Omega$ With V<sub>D1</sub>=+3.0V, V<sub>D2</sub>=+5V

1. Measured in Mini-Circuits characterization test board TB-643+. See characterization Test Circuit (Fig. 2)

Notes

A. Performance and quality attributes and conditions not expressly stated in this specification document are intended to be excluded and do not form a part of this specification document.

B. Electrical specifications and performance data contained in this specification document are based on Mini-Circuit's applicable established test performance criteria and measurement instructions.

C. The parts covered by this specification document are subject to Mini-Circuits standard limited warranty and terms and conditions (collectively, "Standard Terms"); Purchasers of this part are entitled to the rights and benefits contained therein. For a full statement of the Standard Terms and the exclusive rights and remedies thereunder, please visit Mini-Circuits website at www.minicircuits.com/MCLStore/terms.jsp

# **Mini-Circuits**®

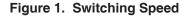

### **Attenuation Switching Specifications**

| Parameter                                                  | Min. | Тур. | Max. | Units |

|------------------------------------------------------------|------|------|------|-------|

| Switching Speed, 50% Control to 0.5dB of Attenuation Value | _    | 1.0  | _    | μSec  |

| Switching Rep Rate                                         | _    | _    | 25   | KHz   |

### **DC Electrical Specifications**

| Parameter            | Min.    | Тур. | Max.    | Units |

|----------------------|---------|------|---------|-------|

| Supply Voltage, VD1  | 2.7     | 3.0  | 3.3     | V     |

| VD2                  | 4.75    | 5.0  | 5.25    | V     |

| Supply Current, ID1* | —       | —    | 100*    | μA    |

| ID2                  | _       | 154  | 186     | mA    |

| Control Input Low**  | —       | _    | 0.3xVD1 | V     |

| Control Input High** | 0.7xVd1 | —    | —       | V     |

| Control Current**    |         | _    | 1       | μΑ    |

\*During turn-on and transition between attenuation states Ind may increase up to 2mA

#### **Absolute Maximum Ratings**

| Parameter                      | Ratings                   |

|--------------------------------|---------------------------|

| Operating Temperature          | -40°C to 85°C             |

| Storage Temperature            | -65°C to 150°C            |

| VD1                            | -0.3V Min., 4V Max.       |

| VD2                            | 6.0V                      |

| Voltage on any control input** | -0.3V Min., VD1+0.3V Max. |

| Input Power                    | +24dBm                    |

\*\*Data, clock or latch enable.

Permanent damage may occur if any of these limits are exceeded.

Notes

Notes A. Performance and quality attributes and conditions not expressly stated in this specification document are intended to be excluded and do not form a part of this specification document. B. Electrical specifications and performance data contained in this specification document are based on Mini-Circuit's applicable established test performance criteria and measurement instructions. C. The parts covered by this specification document are subject to Mini-Circuits trandard limited warranty and terms and conditions (collectivity, "Standard Terms"); Purchasers of this part are entitled to the rights and benefits contained therein. For a full statement of the Standard Terms and the exclusive rights and remedies thereunder, please visit Mini-Circuits' website at www.minicircuits.com/MCLStore/terms.jsp

#

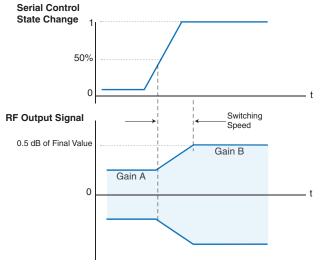

| Pin<br>Number | Function                | Description                                                             |  |

|---------------|-------------------------|-------------------------------------------------------------------------|--|

| 1             | N/C                     | Not Connected                                                           |  |

| 2             | RF IN                   | RF Input Port (Note 1)                                                  |  |

| 3             | N/C                     | Not Connected                                                           |  |

| 4             | N/C                     | Not Connected                                                           |  |

| 5             | DATA                    | Serial Interface Data Input (Note 3)                                    |  |

| 6             | CLOCK                   | Serial Interface Clock Input                                            |  |

| 7             | LE                      | Latch Enable Input (Note 2)                                             |  |

| 8             | V <sub>D1</sub>         | V <sub>D1</sub> Power Supply Input                                      |  |

| 9             | N/C                     | Not Connected                                                           |  |

| 10            | N/C                     | Not Connected                                                           |  |

| 11            | V <sub>D1</sub>         | V <sub>D1</sub> Power Supply Input                                      |  |

| 12            | GND                     | Ground                                                                  |  |

| 13            | V <sub>D1</sub>         | V <sub>D1</sub> Power Supply Input                                      |  |

| 14            | N/C                     | Not Connected                                                           |  |

| 15            | N/C                     | Not Connected                                                           |  |

| 16            | N/C                     | Not Connected                                                           |  |

| 17            | RF OUT &V <sub>D2</sub> | RF output and V <sub>D2</sub> on same pad (external Bias Tee) (Note1,6) |  |

| 18            | N/C                     | Not Connected                                                           |  |

| 19            | BIAS 2                  | Amplifier Bias 2 connects to $V_{_{D2}}$                                |  |

| 20            | BIAS 1                  | Amplifier Bias 1 connects to $V_{D2}$ via inductor(Note1,6)             |  |

| 21            | N/C                     | Not Connected                                                           |  |

| 22            | RF JUMP IN              | Interstage RF Jumper Input (Note 1)                                     |  |

| 23            | RF JUMP OUT             | Interstage RF Jumper Output (Note 1)                                    |  |

| 24            | N/C                     | Not Connected                                                           |  |

| 25            | N/C                     | Not Connected                                                           |  |

| 26            | C8                      | Power Up Control for 8dB Att. Bit (Note 4)                              |  |

| 27            | C4                      | Power Up Control for 4dB Att. Bit (Note 4)                              |  |

| 28            | C2                      | Power Up Control for 2dB Att. Bit (Note 4)                              |  |

| 29            | C1                      | Power Up Control for 1dB Att. Bit (Note 4)                              |  |

| 30            | C0.5                    | Power Up Control for 0.5dB Att. Bit (Note 4)                            |  |

| 31            | C16                     | Power Up Control for 16dB Att. Bit (Note 4)                             |  |

| 32            | N/C                     | Not Connected                                                           |  |

| PADDLE        | GND                     | Ground (Note5)                                                          |  |

#### Table 1. Pad Description

Notes:

1. All RF input and output ports shall be AC coupled with external blocking capacitor.

2. Latch Enable (LE) has an internal 100K $\Omega$  pull-up resistor to  $V_{\text{D1}}$

3. Place a 10K $\Omega$  resistor in series, as close to pin as possible to avoid freq. resonance (see layout drawing PL-355).

4. Refer to Power-up Control Settings.

5. The exposed solder pad on the bottom of the package (See Pin Configuration) must be grounded for proper device operation

6. See application and characterization test circuit and layout drawing PL-355.

A Performance and quality attributes and conditions not expressly stated in this specification document are intended to be excluded and do not form a part of this specification document. B. Electrical specifications and performance data contained in this specification document are based on Mini-Circuit's applicable established test performance criteria and measurement instructions. C. The parts covered by this specification document are subject to Mini-Circuit's tandard limited warranty and terms and conditions (collectively, "Standard Terms"); Purchasers of this part are entitled to the rights and benefits contained therein. For a full statement of the Standard Terms and the exclusive rights and remedies thereunder, please visit Mini-Circuit's website at www.minicircuits.com/MCLStore/terms.jsp

##

Notes

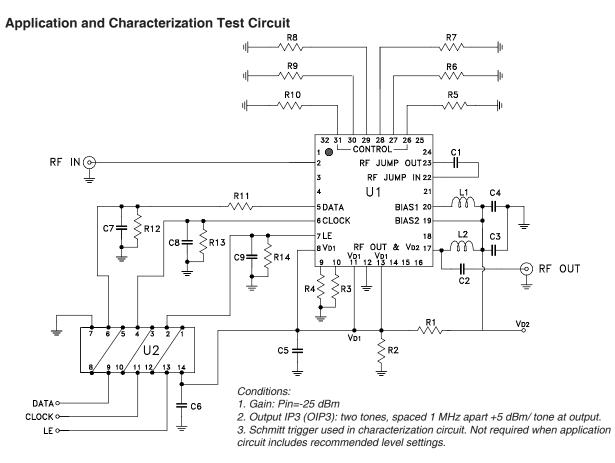

Figure 2. Schematic of Test Circuit used for Characterization. (DUT soldered on Mini-Circuits Characterization Test Board TB-643+). Gain, output power at 1 dB compression (P1dB) Output IP3 (OIP3), Noise Figure are measured using Agilent's N5242A PNA-X Microwave Network Analyzer.

#### **Bill of Materials**

| Ref. Des.      | Value / Description                                | Case Style,<br>Size |

|----------------|----------------------------------------------------|---------------------|

| C1, C4         | 100pF                                              | 0402                |

| C2             | 100pF                                              | 0805                |

| C3             | 1uF                                                | 0805                |

| C5, C7, C8, C9 | 100pF                                              | 0603                |

| C6             | 0.47uF                                             | 0805                |

| L1             | 36nH                                               | 0402                |

| L2             | 47nH                                               | 0402                |

| R1             | 475Ω                                               | 0603                |

| R2             | 681Ω                                               | 0603                |

| R3 ~ R14       | 10kΩ                                               | 0603                |

| U2             | HEX Inverter Trigger<br>Fairchild P/N<br>MM74HC14M |                     |

| U1             | DVGA1-242+                                         |                     |

#### **Product Marking**

A Performance and quality attributes and conditions not expressly stated in this specification document are intended to be excluded and do not form a part of this specification document. B. Electrical specifications and performance data contained in this specification document are based on Min-Circuit's applicable established test performance criteria and measurement instructions. C. The parts covered by this specification document are subject to Min-Circuit's transformations (collectively, "Standard Terms"); Purchasers of this part are entitled to the rights and benefits contained therein. For a full statement of the Standard Terms and the exclusive rights and remedies thereunder, please visit Mini-Circuit's website at www.minicircuits.com/MCLStore/terms.jsp

### **Mini-Circuits**

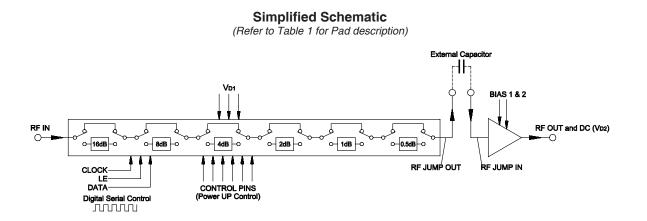

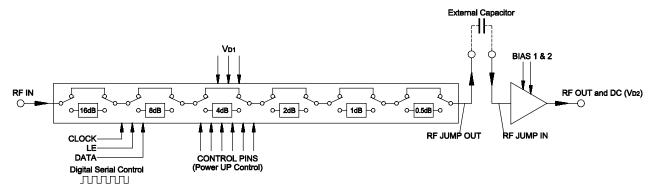

#### **Simplified Schematic**

Figure 3. The DVGA1-242+ Serial interface consists of 6 control bits that select the desired attenuation state, as shown in Table 2 Truth Table.

| Table 2. Truth Table                                                    |     |    |    |    |    |      |

|-------------------------------------------------------------------------|-----|----|----|----|----|------|

| Attenuation<br>State                                                    | C16 | C8 | C4 | C2 | C1 | C0.5 |

| Reference                                                               | 0   | 0  | 0  | 0  | 0  | 0    |

| 0.5 (dB)                                                                | 0   | 0  | 0  | 0  | 0  | 1    |

| 1 (dB)                                                                  | 0   | 0  | 0  | 0  | 1  | 0    |

| 2 (dB)                                                                  | 0   | 0  | 0  | 1  | 0  | 0    |

| 4 (dB)                                                                  | 0   | 0  | 1  | 0  | 0  | 0    |

| 8 (dB)                                                                  | 0   | 1  | 0  | 0  | 0  | 0    |

| 16 (dB)                                                                 | 1   | 0  | 0  | 0  | 0  | 0    |

| 31.5 (dB)                                                               | 1   | 1  | 1  | 1  | 1  | 1    |

| Note: Not all 64 possible combinations of C0.5 - C16 are shown in table |     |    |    |    |    |      |

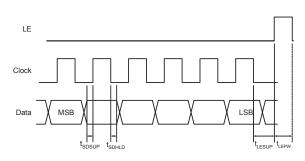

The serial interface is a 6-bit serial in, parallel-out shift register buffered by a transparent latch. It is controlled by three CMOS-compatible signals: Data, Clock, and Latch Enable (LE). The Data and Clock inputs allow data to be serially entered into the shift register, a process that is independent of the state of the LE input. The LE input controls the latch. When LE is HIGH, the latch is transparent and the contents of the serial shift register control the attenuator. When LE is brought LOW, data in the shift register is latched. The shift register should be loaded while LE is held LOW to prevent the attenuator value from changing as data is entered. The LE input should then be toggled HIGH and brought LOW again, latching the new data. The timing for this operation is defined by Figure 4 (Serial Interface Timing Diagram) and Table 3 (Serial Interface AC Characteristics).

Notes A Performance and quality attributes and conditions not expressly stated in this specification document are intended to be excluded and do not form a part of this specification document. B. Electrical specifications and performance data contained in this specification document are based on Mini-Circuit's applicable established test performance criteria and measurement instructions. C. The parts covered by this specification document are subject to Mini-Circuit's tandard limited warranty and terms and conditions (collectively, "Standard Terms"); Purchasers of this part are entitled to the rights and benefits contained therein. For a full statement of the Standard Terms and the exclusive rights and remedies thereunder, please visit Mini-Circuit's website at www.minicircuits.com/MCLStore/terms.jsp

## **Mini-Circuits**

Figure 4. Serial Interface Timing Diagram

| Symbol                                                                                                                                                     | Parameter                                        | Min. | Max. | Units |

|------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|------|------|-------|

| <b>f</b> <sub>clk</sub>                                                                                                                                    | Serial data clock<br>frequency (Note 1)          |      | 10   | MHz   |

| t <sub>clkH</sub>                                                                                                                                          | Serial clock HIGH time                           | 30   |      | ns    |

| t <sub>clkL</sub>                                                                                                                                          | Serial clock LOW time                            | 30   |      | ns    |

| t <sub>LESUP</sub>                                                                                                                                         | LE set-up time after last<br>clock falling edge  | 10   |      | ns    |

| t <sub>LEPW</sub>                                                                                                                                          | LE minimum pulse width                           | 30   |      | ns    |

| t <sub>SDSUP</sub>                                                                                                                                         | Serial data set-up time before clock rising edge | 10   |      | ns    |

| t <sub>sDHLD</sub>                                                                                                                                         | Serial data hold time 10 ns                      |      | ns   |       |

| Note 1. fclk verified during the functional pattern test. Serial programming sections of the functional pattern are clocked at 10MHz to verify fclk speci- |                                                  |      |      |       |

#### Table 3. Serial Interface AC Characteristics (VD1=3V)

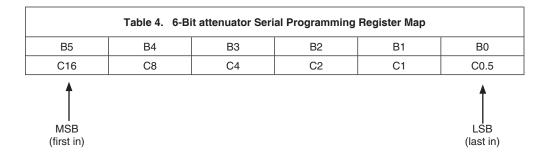

The DVGA1-242+, uses a common 6-bit serial, as shown in Table 4: 6-Bit attenuator Serial Programming Register Map. The first bit, the MSB, corresponds to the 16-dB Step and the last bit, the LSB, corresponds to the 0.5dB step.

fication.

#### **Power-up Control Settings**

The DVGA1-242+ always assumes a specifiable attenuation setting on power-up, allowing a known attenuation state to be established before an initial serial control word is provided. When the attenuator powers up, the six control bits are set to whatever data is present on the six control inputs (C0.5 to C16). This allows any one of the 64 attenuation settings to be specified as the power-up state.

A Performance and quality attributes and conditions not expressly stated in this specification document are intended to be excluded and do not form a part of this specification document. B. Electrical specifications and performance data contained in this specification document are based on Min-Circuit's applicable established test performance criteria and measurement instructions. C. The parts covered by this specification document are subject to Min-Circuit's transformations (collectively, "Standard Terms"); Purchasers of this part are entitled to the rights and benefits contained therein. For a full statement of the Standard Terms and the exclusive rights and remedies thereunder, please visit Mini-Circuit's website at www.minicircuits.com/MCLStore/terms.jsp

| Additional Detailed Technical Information<br>additional information is available on our dash board. To access this information <u>click here</u> |                                                               |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|--|--|--|

|                                                                                                                                                  | Data Table                                                    |  |  |  |

| Performance Data                                                                                                                                 | Swept Graphs                                                  |  |  |  |

|                                                                                                                                                  | S-Parameter (S2P Files) Data Set (.zip file)                  |  |  |  |

| Case Style                                                                                                                                       | DG1677 Plastic package, exposed paddle, lead finish: Ni/Pd/Au |  |  |  |

| Tape & Reel     Standard quantities available on reel                                                                                            | F68<br>7" reels with 20,50,100,200, 500 or 1K devices         |  |  |  |

| Suggested Layout for PCB Design                                                                                                                  | PL-355                                                        |  |  |  |

| Evaluation Board                                                                                                                                 | TB-643+                                                       |  |  |  |

| Environmental Ratings                                                                                                                            | ENV66                                                         |  |  |  |

### **ESD** Rating

Human Body Model (HBM): Class 1A (250 to <500V) in accordance with ANSI/ESD STM 5.1 - 2001

Machine Model (MM): Class M1 (40V) in accordance with ANSI/ESD STM5.2-1999

#### **MSL Rating**

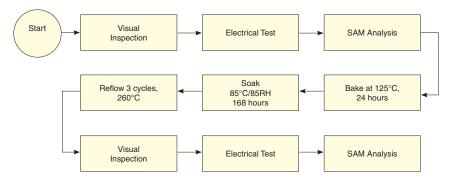

Moisture Sensitivity: MSL1 in accordance with IPC/JEDEC J-STD-020D

### **MSL Test Flow Chart**

Notes

A Performance and quality attributes and conditions not expressly stated in this specification document are intended to be excluded and do not form a part of this specification document. B. Electrical specifications and performance data contained in this specification document are based on Min-Circuit's applicable established test performance criteria and measurement instructions. C. The parts covered by this specification document are subject to Min-Circuits andard limited warranty and terms and conditions (collectively, "Standard Terms"); Purchasers of this part are entitled to the rights and benefits contained therein. For a full statement of the Standard Terms and the exclusive rights and remedies thereunder, please visit Mini-Circuits' website at www.minicircuits.com/MCLStore/terms.jsp

#

www.minicircuits.com P.O. Box 35166, Brooklyn, NY 11235-0003 (718) 934-4500 sales@minicircuits.com